文章来源:半导体与物理

原文作者:jjfly686

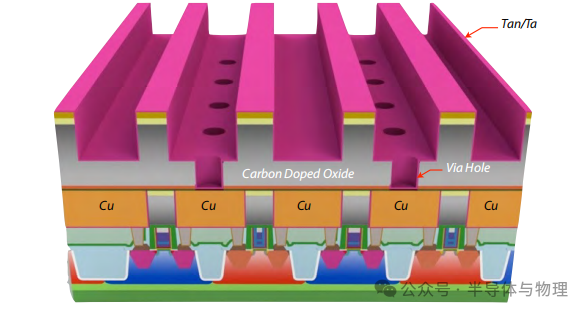

本文介绍了在芯片铜互连工艺中需要阻挡层的原因以及关键工艺流程。

为什么需要阻挡层?

在芯片的铜互连工艺中,铜原子极易向周围的绝缘介质(如SiO₂或Low-K材料)扩散,导致电路短路或漏电失效。为了阻止这种扩散,必须在铜与介质之间沉积一层纳米级阻挡层。氮化钽(TaN)因其高致密性、抗扩散能力和导电性,成为主流选择。然而,随着制程进入28 nm以下节点,阻挡层的均匀性和覆盖性面临巨大挑战。

物理气相沉积(PVD)技术:

在22 nm和14 nm节点,PVD仍是阻挡层沉积的核心技术,其优势与创新如下:

离子化金属等离子体PVD

通过高能离子轰击钽靶材,溅射出钽原子并与氮气反应生成TaN薄膜。再溅射(Re-sputter)工艺。在沉积TaN后,用氩离子轰击薄膜表面,将底部的TaN重新分布到侧壁,显著提升深宽比>5:1的通孔覆盖率(如32 nm节点侧壁覆盖提升40%)。

工艺优势

TaN薄膜(2-5 nm)的沉积速率可达10 nm/min,适合量产;无需碳基前驱体,避免ALD工艺中的碳残留问题;设备成熟,单次工艺成本比ALD低30%以上。

局限性

深孔底部覆盖率不足,需结合溅射清洗(Sputter Clean)去除残留污染物;10 nm以下线宽中,PVD的台阶覆盖率(<50%)难以满足需求。

原子层沉积(ALD)

ALD虽在理论上具备原子级精度,但在实际应用中仍面临多重挑战:

ALD TaN的工艺瓶颈

前驱体污染:使用有机钽源(如Ta(NMe₂)₅)和氨气(NH₃)反应时,碳残留会导致薄膜电阻率升高(比PVD TaN高3倍);空间位阻效应:在深宽比>10:1的结构中,前驱体分子无法有效扩散至底部,导致薄膜不连续;沉积速率低:ALD单循环仅生长0.1 nm,沉积5 nm薄膜需50次循环,耗时是PVD的10倍。

潜在优势与未来应用

ALD可在3D FinFET侧壁实现±0.2 nm的厚度控制;

随着线宽缩至5 nm,ALD可能成为唯一满足覆盖性要求的技术。

关键工艺流程解析(以28 nm双大马士革结构为例)

目的:去除通孔内的铜氧化物和刻蚀残留。

方法:硝酸/氢氟酸(HNO₃/HF)混合溶液腐蚀,随后200℃烘烤去除水分。

参数:软性氩离子轰击(能量<50 eV),清除底部残留污染物,提升TaN附着力。

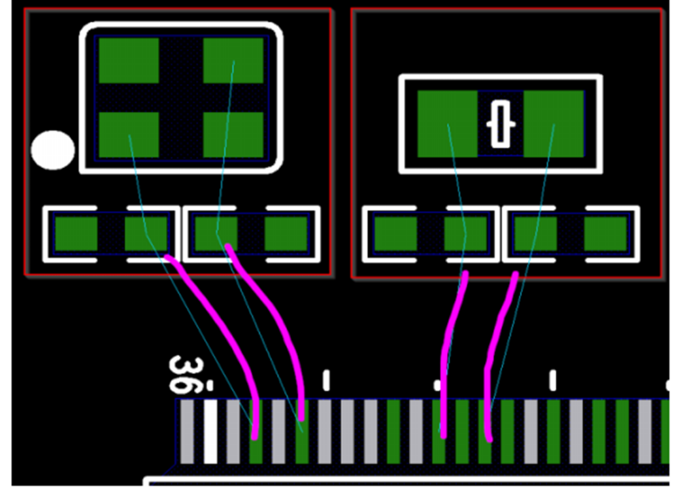

PVD沉积:沉积2 nm TaN层,随后氩离子再溅射,将底部TaN重新分布至侧壁(覆盖率从60%提升至85%)。

作用:作为铜种子层的黏附层,厚度1-2 nm,防止铜剥离。

工艺:PVD沉积300 nm铜层,为后续电镀铜填充提供导电基底。

化学清洗(Chemical Clean)

溅射清洗(Sputter Clean)

TaN沉积与再溅射

钽(Ta)层沉积

铜种子层(Cu Seed)沉积