单芯片解决方案,开启全新体验——W55MH32 高性能以太网单片机

W55MH32是WIZnet重磅推出的高性能以太网单片机,它为用户带来前所未有的集成化体验。这颗芯片将强大的组件集于一身,具体来说,一颗W55MH32内置高性能Arm® Cortex-M3核心,其主频最高可达216MHz;配备1024KB FLASH与96KB SRAM,满足存储与数据处理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP协议栈、内置MAC以及PHY,拥有独立的32KB以太网收发缓存,可供8个独立硬件socket使用。如此配置,真正实现了All-in-One解决方案,为开发者提供极大便利。

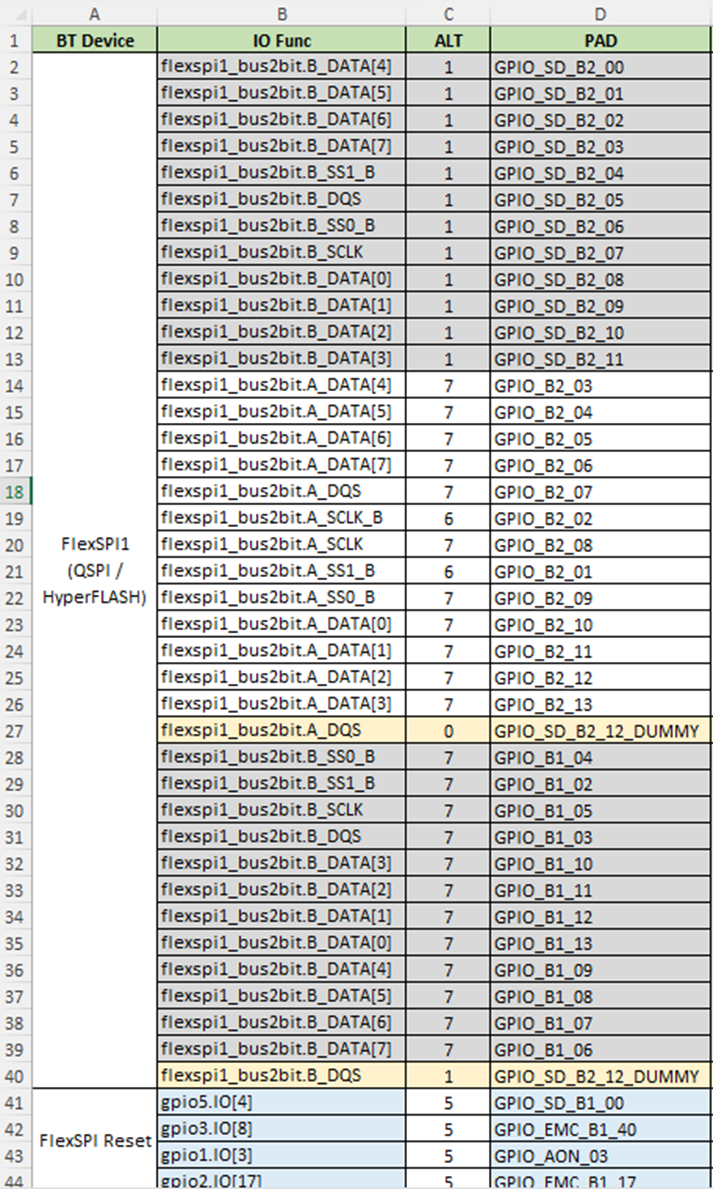

在封装规格上,W55MH32 提供了两种选择:QFN68和QFN100。

W55MH32Q采用QFN68封装版本,尺寸为8x8mm,它拥有36个GPIO、3个ADC、12通道DMA、17个定时器、2个I2C、3个串口、2个SPI接口(其中1个带I2S接口复用)、1个CAN以及1个USB2.0。在保持与同系列其他版本一致的核心性能基础上,仅减少了部分GPIO以及SDIO接口,其他参数保持一致,性价比优势显著,尤其适合网关模组等对空间布局要求较高的场景。紧凑的尺寸和精简化外设配置,使其能够在有限空间内实现高效的网络连接与数据交互,成为物联网网关、边缘计算节点等紧凑型设备的理想选择。 同系列还有QFN100封装的W55MH32L版本,该版本拥有更丰富的外设资源,适用于需要多接口扩展的复杂工控场景,软件使用方法一致。更多信息和资料请进入http://www.w5500.com/网站或者私信获取。

此外,本W55MH32支持硬件加密算法单元,WIZnet还推出TOE+SSL应用,涵盖TCP SSL、HTTP SSL以及MQTT SSL等,为网络通信安全再添保障。

为助力开发者快速上手与深入开发,基于W55MH32Q这颗芯片,WIZnet精心打造了配套开发板。开发板集成WIZ-Link芯片,借助一根USB C口数据线,就能轻松实现调试、下载以及串口打印日志等功能。开发板将所有外设全部引出,拓展功能也大幅提升,便于开发者全面评估芯片性能。

若您想获取芯片和开发板的更多详细信息,包括产品特性、技术参数以及价格等,欢迎访问官方网页:http://www.w5500.com/,我们期待与您共同探索W55MH32的无限可能。

第十章 基本定时器

W55MH32微控制器集成了丰富的定时器资源,共计17个定时器,包括:10个通用16位定时器(每定时器支持4通道输入捕获/输出比较/PWM/脉冲计数及增量编码器接口)、2个带死区控制和紧急刹车功能的16位高级控制定时器(专为电机控制优化)、2个看门狗定时器(独立型和窗口型)、1个24位系统时间定时器(递减计数)以及2个16位基本定时器,全面覆盖工业控制、电机驱动、系统监控及实时计数等应用场景。

本章分为如下几个小节:

1 基本定时器 简介

2 寄存器描述

1 基本定时器简介

W55MH32的基本定时器为TIM6和TIM7。

1.1 TIM6和TIM7简介

基本定时器 TIM6 和 TIM7 各包含一个 16 位自动装载计数器,由各自的可编程预分频器驱动。它们可以作为通用定时器提供时间基准,特别地可以为数模转换器(DAC)提供时钟。实际上,它们在芯片内部直接连接到 DAC 并通过触发输出直接驱动 DAC。这 2 个定时器是互相独立的,不共享任何资源。

1.2 TIM6和TIM7的主要特性

TIM6和TIM7 定时器的主要功能包括:

16 位自动重装载累加计数器。

16 位可编程(可实时修改)预分频器,用于对输入的时钟按系数为 1~65536 之间的任意数值分频。

触发DAC的同步电路。

在更新事件(计数器溢出)时产生中断请求。

基本定时器框图

1.3 TIM6和TIM7的功能

时基单元

这个可编程定时器的主要部分是一个带有自动重装载的 16 位累加计数器,计数器的时钟通过一个预分频器得到。

软件可以读写计数器、自动重装载寄存器和预分频寄存器,即使计数器运行时也可以操作。时基单元包含:

计数器寄存器(TIMx_CNT)

预分频寄存器(TIMx_PSC)

自动重装载寄存器(TIMx_ARR)

自动重装载寄存器是预加载的,每次读写自动重装载寄存器时,实际上是通过读写预加载寄存器实现。根据 TIMx_CR1 寄存器中的自动重装载预加载使能位(ARPE),写入预加载寄存器的内容能够立即或在每次更新事件时,传送到它的影子寄存器。当 TIMx_CR1 寄存器的 UDIS 位为'0',则每当计数器达到溢出值时,硬件发出更新事件;软件也可以产生更新事件;关于更新事件的产生,随后会有详细的介绍。计数器由预分频输出 CK_CNT 驱动,设置 TIMx_CR1 寄存器中的计数器使能位(CEN)使能计数器计数。

注意: 实际的设置计数器使能信号 CNT_EN 相对于 CEN 滞后一个时钟周期。

预分频器

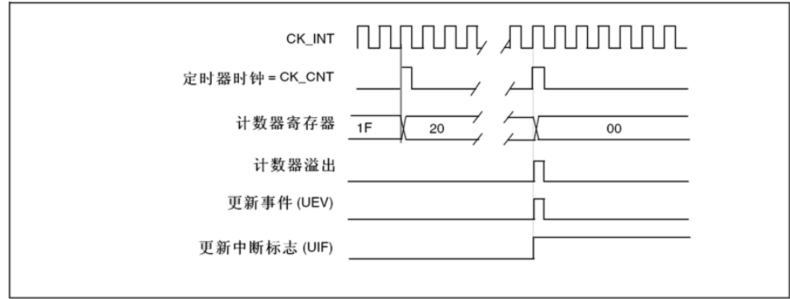

预分频可以以系数介于 1 至 65536 之间的任意数值对计数器时钟分频。它是通过一个 16 位寄存器(TIMx_PSC)的计数实现分频。因为 TIMx_PSC 控制寄存器具有缓冲,可以在运行过程中改变它的数值,新的预分频数值将在下一个更新事件时起作用。以下两图是在运行过程中改变预分频系数的例子。

预分频系数从 1 变到 2 的计数器时序图

预分频系数从 1 变到 4 的计数器时序图

计数模式

计数器从 0 累加计数到自动重装载数值(TIMx_ARR 寄存器),然后重新从 0 开始计数并产生一个计数器溢出事件。每次计数器溢出时可以产生更新事件;(通过软件或使用从模式控制器)设置 TIMx_EGR 寄存器的UG 位也可以产生更新事件。设置 TIMx_CR1 中的 UDIS 位可以禁止产生 UEV 事件,这可以避免在写入预加载寄存器时更改影子寄存器。在清除 UDIS 位为'0'之前,将不再产生更新事件,但计数器和预分频器依然会在应产生更新事件时重新从 0 开始计数(但预分频系数不变)。另外,如果设置了 TIMx_CR1 寄存器中的 URS(选择更新请求),设置 UG 位可以产生一次更新事件 UEV,但不设置 UIF 标志(即没有中断)。当发生一次更新事件时,所有寄存器会被更新并(根据 URS位)设置更新标志(TIMx_SR寄存器的 UIF位):

传送预装载值(TIMx_PSC 寄存器的内容)至预分频器的缓冲区。

自动重装载影子寄存器被更新为预装载值(TIMx_ARR)。

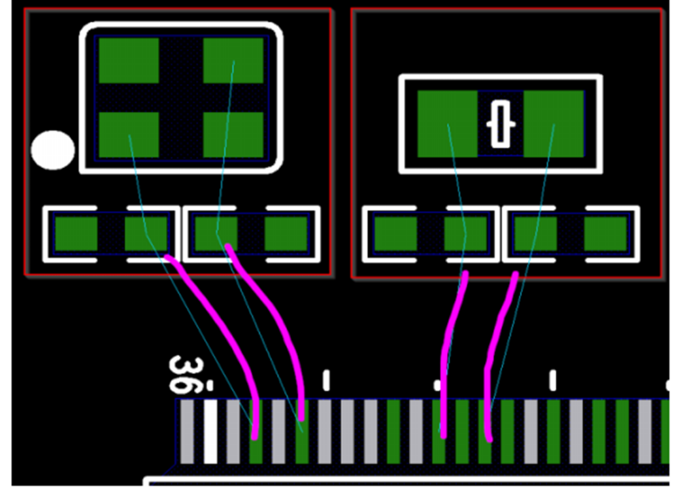

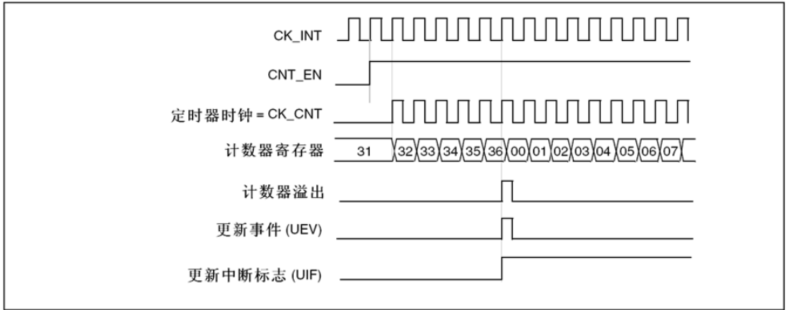

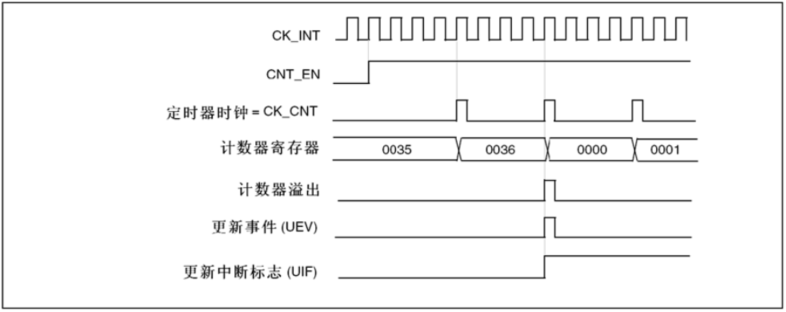

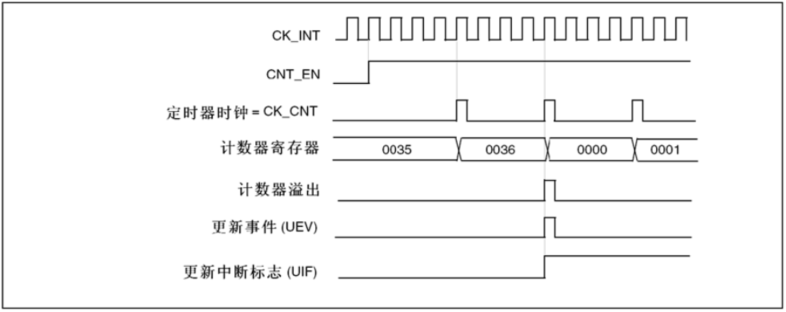

以下是一些在 TIMx_ARR=0x36 时不同时钟频率下计数器工作的图示例子。

计数器时序图,内部时钟分频系数为 1

计数器时序图,内部时钟分频系数为 2

计数器时序图,内部时钟分频系数为 4

计数器时序图,内部时钟分频系数为 N

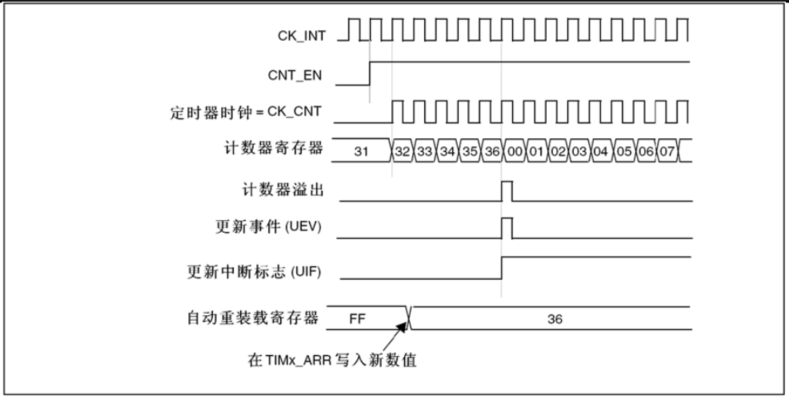

计数器时序图,当 ARPE=0 时的更新事件(TIMx_ARR 没有预装载)

计数器时序图,当 ARPE=1 时的更新事件(预装载 TIMx_ARR)

时钟源

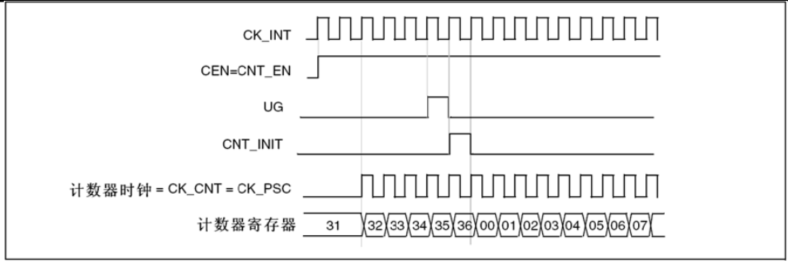

计数器的时钟由内部时钟(CK_INT)提供。TIMx_CR1 寄存器的 CEN 位和 TIMx_EGR 寄存器的 UG 位是实际的控制位,(除了 UG 位被自动清除外)只能通过软件改变它们。一旦置 CEN 位为'1',内部时钟即向预分频器提供时钟。下图示出控制电路和向上计数器在普通模式下,没有预分频器时的操作。

普通模式时序图,内部时钟分频系数为 1

1.4 调试模式

当微控制器进入调试模式(Cortex-M3 核心停止)时,根据 DBG 模块中的配置位 DBG_TIMx_STOP 的设置,TIMx 计数器或者继续计数或者停止工作。

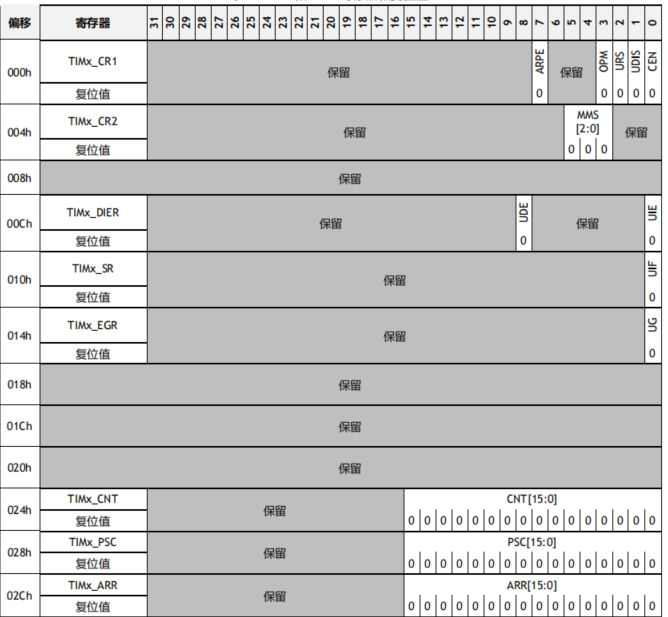

2 寄存器描述

TIM6 和 TIM7 寄存器:可以用半字(16 位)或字(32 位)的方式操作这些外设寄存器。

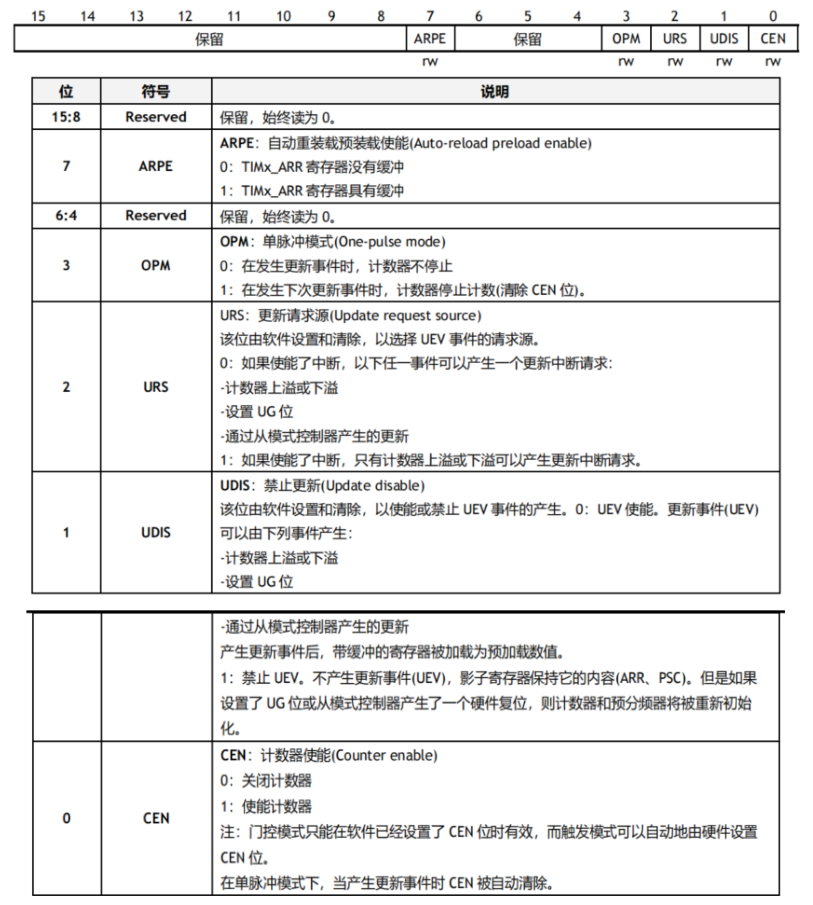

2.1 TIM6和TIM7控制寄存器 1(TIMx_CR1)

偏移地址:0x00

复位值:0x0000

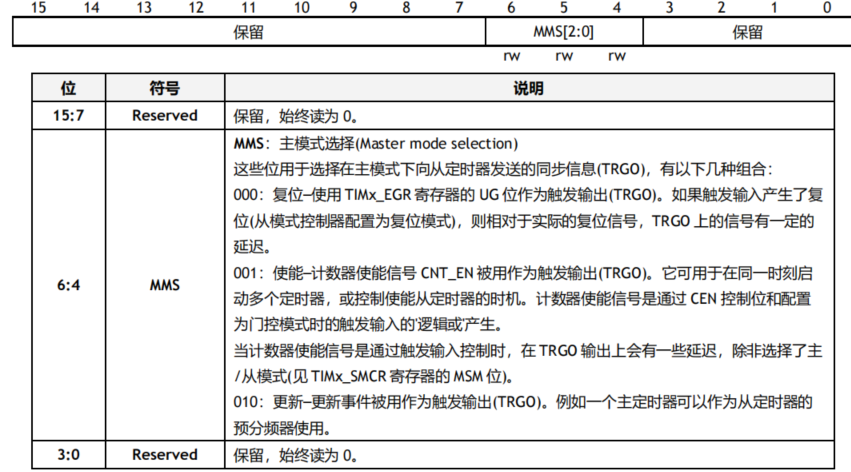

2.2 TIM6和TIM7控制寄存器 2(TIMx_CR2)

偏移地址:0x04

复位值:0x0000

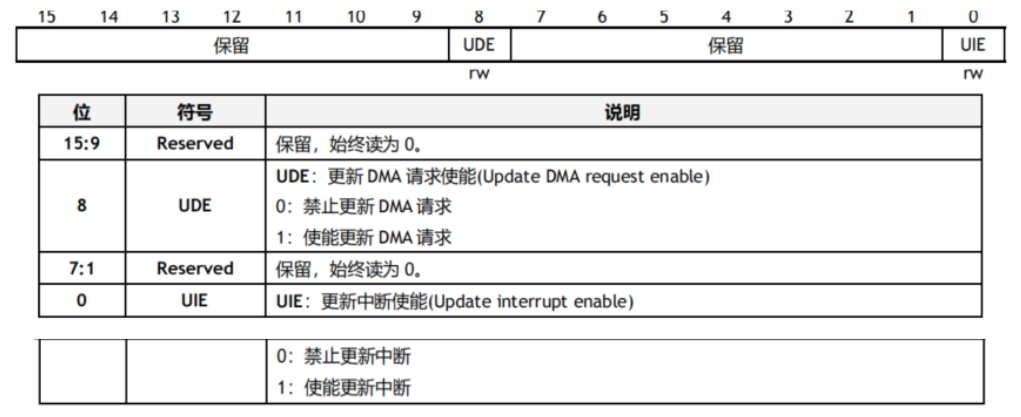

2.3 TIM6和TIM7DMA/中断使能寄存器(TIMx_DIER)

偏移地址:0x0C

复位值:0x0000

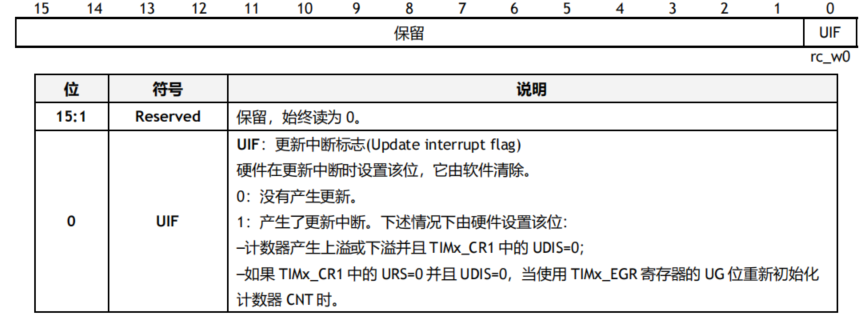

2.4 TIM6和TIM7状态寄存器(TIMx_SR)

偏移地址:0x10

复位值:0x0000

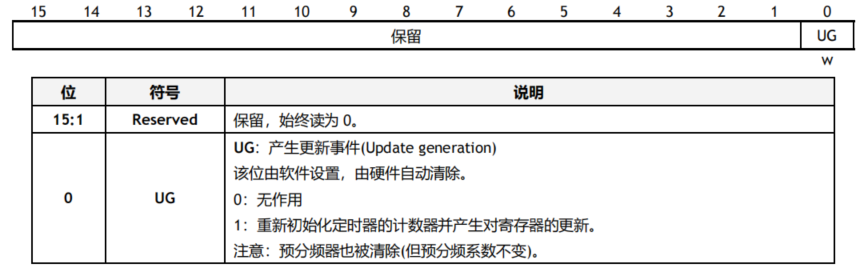

2.5 TIM6和TIM7事件产生寄存器(TIMx_EGR)

偏移地址:0x14

复位值:0x0000

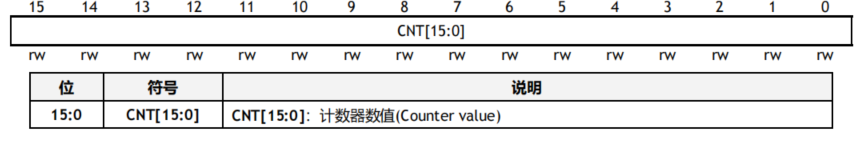

2.6 TIM6和TIM7计数器(TIMx_CNT)

偏移地址:0x24

复位值:0x0000

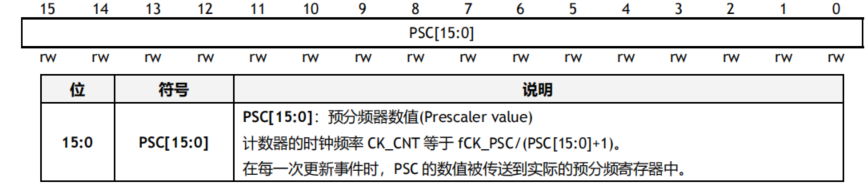

2.7 TIM6和TIM7预分频器(TIMx_PSC)

偏移地址:0x28

复位值:0x0000

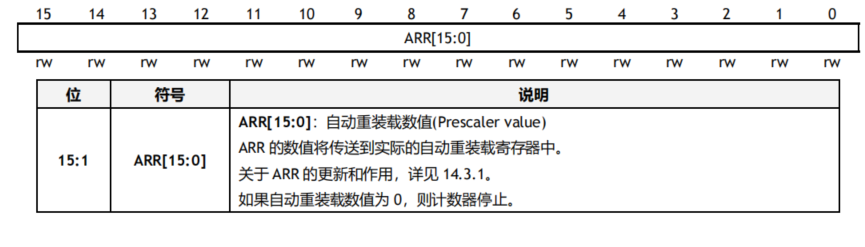

2.8 TIM6和TIM7自动重装载寄存器(TIMx_ARR)

2.9 TIM6和TIM7寄存器

下表中将 TIMx 的所有寄存器映射到一个 16 位可寻址(编址)空间。

WIZnet 是一家无晶圆厂半导体公司,成立于 1998 年。产品包括互联网处理器 iMCU™,它采用 TOE(TCP/IP 卸载引擎)技术,基于独特的专利全硬连线 TCP/IP。iMCU™ 面向各种应用中的嵌入式互联网设备。

WIZnet 在全球拥有 70 多家分销商,在香港、韩国、美国设有办事处,提供技术支持和产品营销。

香港办事处管理的区域包括:澳大利亚、印度、土耳其、亚洲(韩国和日本除外)。

审核编辑 黄宇